ترانزیستور اثر میدان پیوندی (JFET)

ترانزیستور اثر میدان پیوندی (JFET)

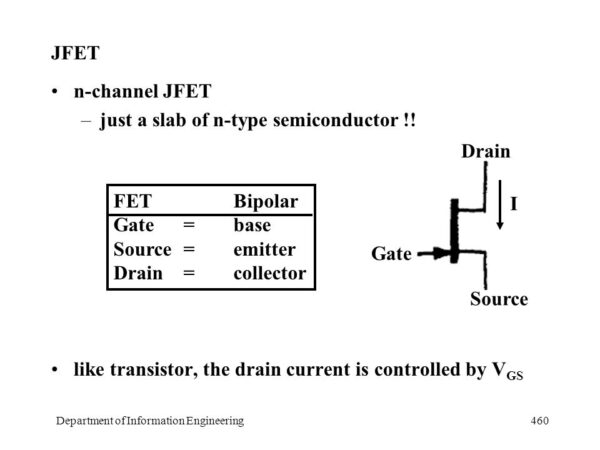

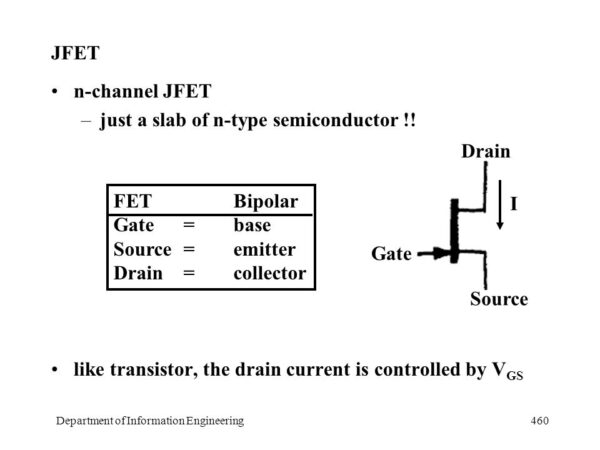

ترانزیستور اثر میدان پیوندی یا Junction Field Effect Transistor :

نوعی از ترانزیستور های فت (fet) بوده ، که برای کاربرد خاصی طراحی شده اند.این ترانزیستور ها دارای دو دسته اِن چَنل (N CHANNEL) و پی چَنل (P CHANNEL) می باشند.

ساختمان JFET با کانال N :

شکل زیر ساختمان این نوع ترانزیستور را نشان می دهد:

این ترانزیستور از یک کریستال نوع N تشکیل شده است که یک فلز ۳ ظزفیتی مانند ایندیم را به گونه ای نفوذ می دهند که یک ناحیه نوع p با غلظتی بیش از ناحیه n تشکیل شود تا یک پیوند PN بوجود آید.

در این حالت ناحیه N را کانال و نیمه هادی نوع P را دروازه یا گیت ( Gate ) می نامند. با اتصال دو سیم به دو طرف لایه N و یک سیم به لایه P یک عنصر سه پایه حاصل می شود که به ترانزیستور با اثر میدان پیوندی معروف است.

در عمل برای این که ترانزیستور مشخصات الکتریکی بهتری داشته باشد ، ناحیه گیت را مانند شکل زیر در اطراف کانال ایجاد می کنند.

در این ترانزیستور دو کریستال P را از داخل به هم وصل می کنند ، چنانچه ترانزیستوری با دو گیت در دست باشد ، باید به وسیله سیمی این دو پایه را به هم وصل نمود . ممکن است برای سادگی رسم شکل ، دو کریستال P را که به هم متصل است فقط با یک اتصال گیت ، نشان دهند.

ساختمان JFET با کانال P :

ساختمان JFET با کانال P شبیه JFET با کانال N است، با این تفاوت که جنس کانال از نوع کریستال P و جنس گیت از کریستال N است. در شکل زیر ساختمان کریستالی و علامت اختصاری JFET با کانال P را مشاهده می کنید:

رفتار ترانزیستور اثر میدان پیوندی (JFET) در مدار:

برای بررسی رفتار ترانزیستور در مدار ، نخست حالتی را در نظر می گیریم که پایه گیت به پایه سورس اتصال کوتاه شده باشد. در این حالت اثر تغییر VDS را روی کانال بررسی می کنیم.

مطابق شکل زیر اگر پایه های درین سورس نیز اتصال کوتاه شده باشند ، هیچ جریانی از کانال نمی گذرد و نواحی P و N توسط لایه نازک سد که تهی از حامل های جریان است و بلافاصله پس از ایجاد پیوند PN به وجود می آید ، از یکدیگر جدا می شوند.

حال اگر یک منبع ولتاژ به نام VDD را بین پایه های درین و سورس وصل کنیم ، به طوری که درین نسبت به سورس مثبت باشد ، با افزایش تدریجی ولتاژ ، جریانی که از کانال می گذرد نیز افزایش می یابد.

اعمال این ولتاژ بین درین و سورس و عبور جریان از آن ، افت ولتاژی را در مسیر به وجود می آورد و پیوند PN را در گرایش معکوس قرار می دهد.

در این حالت ناحیه تهی شده از حامل های جریان بیشتر در داخل کانال نفوذ می کند. شکل زیر ، ناحیه تهی از بار P و N ( افزایش لایه سد ) در اثر افزایش جریان درین را نشان می دهد.

ترانزیستور اثر میدان پیوندی (JFET):

گسترش ناحیه تهی از بار در اثر توزیع پتانسیل VDS از درین تا سورس است. چون گیت در پتانسیل صفر قرار دارد و هم پتانسیل با سورس است، هرقدر در طول کانال به درین نزدیک تر شویم ، اختلاف پتانسیل آن نسبت به گیت بیش تر می شود ، زیرا در طول میله مانند افت ولتاژ در یک مقاومت است.

در این شرایط اتصال PN بیشتر به بایاس مخالف میل می کند و لایه تهی از بار گسترده تر می شود. به بیان دیگر توسعه ناحیه تهی از بار ( گسترش ناحیه سد) از سمت درین رشد می کند.

چنانچه VDS را باز هم افزایش دهیم ، ناحیه تهی شده گسترش بیشتری می یابد و سرانجام مطابق شکل زیر به حداکثر گسترش خود می رسد.

تا زمانی که کانال به حد اکثر گرفتگی نرسیده است ، افزایش VDS سبب افزایش جریان درین ID می شود. با بسته شدن حداکثری کانال ، دیگر افزایش VDS تغییر محسوسی در جریان درین ایجاد نمی کند و جریان درین ثابت می ماند ، در این حالت می گویند JFET به اشباع رسیده است.

جریان اشباع را IDSS ( جریان درین سورس اشباع ) می نامند. افزایش بیشتر VDS ، ناحیه تهی از بار در سطح کانال را گسترده تر می کند و مقاومت کانال افزایش می دهد. چون میزان افزایش VDS و افزایش مقاومت کانال ( RDS ) به یک نسبت است، جریان درین همچنان ثابت باقی می ماند.

همان طور در شکل زیر مشاهده می کنید ، افزایش VDS بعد از بسته شدن حداکثری کانال ، تاثیری در مقدار ID ندارد و ID در حد مقدار IDSS ثابت باقی مانده است.

چنان چه با اعمال یک ولتاژ به دو سر گیت سورس سد PN را در گرایش معکوس قرار دهیم ، هرگونه افزایشی در میزان این ولتاژ ، گسترش سریع تر لایه سد ( ناحیه تهی از حامل های جریان ) در داخل کانال را به همراه داردو موجب افزایش مقاومت کانال و کاهش جریان درین می شود.

با کاهش VGG ، عرض کانال بیشتر می شود و مقاومت کانال را کاهش می دهد. در این شرایط جریان درین بیشتری از مدار می گذرد.

مقدار VGS را افزایش داده ایم. در این حالت، کانال باریک تر می شود و مقاومت کانال را افزایش می دهد. لذا جریان درین ( ID ) کمتری از مدار می گذرد.

اصطلاحات و تعاریف متداول :

منحنی مشخصه ترانزیستور اثر میدان پیوندی (JFET) :

برای این که بتوانیم هر قطعه ی الکترونیکی را تحلیل و بررسی کنیم باید منحنی مشخصه های را در مورد آن بدانیم. این منحنی مشخصه ها را رابطه ی بین ولتاژ و جریان پایه ها را بررسی می کنند.

در ترانزیستور JFET تغییرات جریان درین وابسته به تغییرات دو عامل است که یکی VDS و دیگری VGS می باشد. برای مشخص کردن میزان این وابستگی ها باید در هر مرحله یکی از این متغیر ها را ثابت نگه داریم و دیگری را تغییر دهیم و مجهول را بررسی کنیم.

منحنی مشخصه ی خروجی JFET:

برای رسم منحنی مشخصه ی خروجی این ترانزیستور باید اثر تغییرات ولتاژ VDS را بر جریان IS به ازای ولتاژ های مختلف VGS بررسی کنیم.

برای این کار می توانیم در هر مرحله ولتاژ VGS را رو ی یک مقدار مشخص تنطیم کنیم و سپس با تغییر VDS از صفر تا حداکثر جریان IS را بررسی کنیم.

نواحی کار منحنی مشخصه ی خروجی ترانزیستور اثر میدان پیوندی (JFET):

در این قسمت نواحی مختلف ای ترانزیستور و حالت های کاری که ترانزیستور می تواند روی آن قرار بگیرد را بررسی می کنیم:

ناحیه قطع ( Cut off Region )

ناحیه قطع ناحیه ای است که در آن ولتاژ VGS برابر با VGS off می باشد. در این حالت کانال داخل ترانزیستور بسته می شود و جریان ID برابر با صفر است و با تغییرات VDS این مقدار جریان تغییر نمی کند.

در این حالت ترانزیستور اثر میدان پیوندی (JFET) به صورت یک کلید قطع عمل می کند.

ناحیه اهمی ( Ohmic Region )

این بخش ناحیه ای از منحنی مشخصه خروجی بخش است که در آن تغییرات جریان ID نسبت به VDS خطی است. در این ناحیه ترانزیستور مانند یک مقاومت اهمی تابع ولتاژ عمل می کند که مقدار آن با ولتاژ گیت سورس کنترل می شود.

ناحیه اشباع یا فعال ( Active Region ) :

در ناحیه ای که در آن VDS > Vr می باشد ناحیه اشباع یا فعال می گویند. در این ناحیه تغییرات VDS اثری بر مقدار ID ندارد و جریان درین تقریبا ثابت است.

شکل زیر محدوده این ناحیه را بر روی منحنی مشخصه ی خروجی نشان می دهد :

برای آن که ترانزیستور از ناحیه اهمی وارد ناحیه اشباع (فعال) شود باید مقدار ولتاژ درین سورس از مقدار معینی که ولتاژ درین سورس گذر ( Transition Voltage ) ( VDstr ) نامیده می شود ، بیشتر باشد یعنی VDS > VDS(Tr) .

منحنی مشخصه ی انتقالی ترانزیستور اثر میدان پیوندی (JFET):

در منحنی مشخصه ی انتقالی ، تغییرات VGS را بر ID بررسی می کنیم. مقدار VGS می تواند از صفر ولت تا مقدار VGS off تغییر کند. این تغییرات ولتاژ ، جریان درین را از ID = 0 تا IDSS کنترل می کند. به همین دلیل نسبت بین دو کمیت ID برحسب تغییرات VGS در شرایطی که VDS ثابت است را منحنی مشخصه انتقالی می گویند. در شکل زیر منحنی مشخصه ی انتقالی برای یک نوع JFET با کانال N رسم شده است :

(منبع : microlearn )

اولین دیدگاه را ثبت کنید