گیت های منطقی

گیت های منطقی

گیت های منطقی در حقیقت یک مدار الکترونیکی است که یک یا چند ورودی و فقط یک خروجی دارد. شکل زیر بلوک دیاگرام دروازه منطقی را نشان می دهد.

گیت های منطقی یک خروجی دارند و چند ورودی که خروجی آن ها بسته به ورودی آن های تغییر می کند و در وضعیت Low یا High قرار می گیرد.

گیت های منطقی دو گروه هستند ، گیت های پایه و گیت های ترکیبی که از گیت های پای ساخته می شوند. گیت هایی که در زیر بیان می کنیم دارای دو ورودی هستند و می توانند بیشتر از یک ورودی نیز داشته باشند.

دروازه های منطقی پایه:

۱- گیت OR ( یا )

ساختمان گیت OR با دو ورودی را با استفاده از دیود ایده آل در شکل زیر مشاهده می کنید:

در مدار شکل بالا که ساختمان دیودی گیت OR را نشان می دهد ، اگر به هر دو ورودی A و B ولتاژ Low را اعمال کنیم ، دیود ها به حالت قطع می روند و خروجی مدار در حالت Low قرار می گیرد. همچنین اگر یکی از ورودی ها را در حالت High قرار دهیم و دیگری را در حالت Low قرار دهیم خروجی در حالت High قرار می گیرد. حال اگر هر دو ورودی را در حالت high قرار دهیم ، خروجی در حالت High قرار می گیرد.

پس نتیجه گرفتیم در این گیت ، خروجی گیت رمانی در وضعیت ۱ قرار می گیرد که دست کم یکی از ورودی های آن در وضعیت ۱ منطقی قرار گیرند.

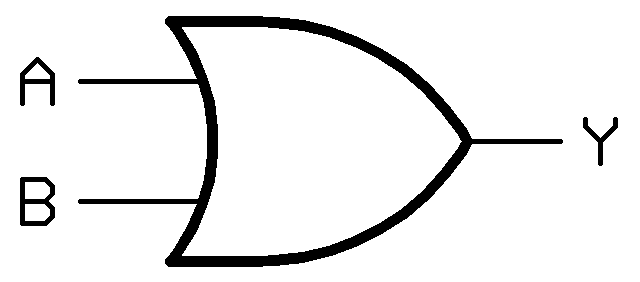

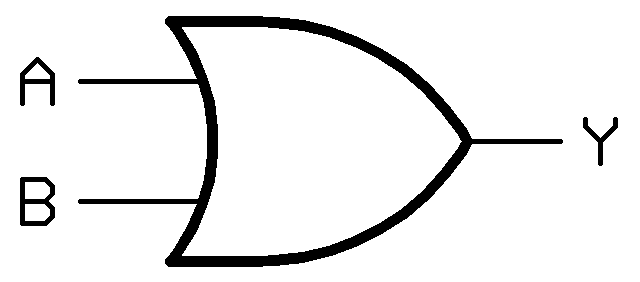

در شکل زیر نماد استاندارد بین المللی و آمریکایی گیت OR را مشاهده می کنید:

همچنین در استاندارد انگلیسی نماد گیت OR به صورت زیر است :

برای هر گیت می توان جدول صحت یا جدول درستی تعریف کرد و مقادیر ورودی و خروجی را براساس صفر و یک منطقی در آن نشان داد.

برای اینکه نشان دهیم متغیر A و متغیر B با یکدیگر OR شده اند ، از رابطه زیر استفاده می کنیم :

یک دروازه OR می تواند بیش از دو ورودی داشته باشد ، برای مثال در شکل زیر شما مدار معادل کلیدی و نماد گیت OR با سه ورودی را مشاهده می کنید :

همانطور که در جلسه قبل گفته شد ، گیت های منطقی به صورت آی سی های در وازه منطقی وجود دارند و به صورت یک پکیج در آی سی موجود اند. در شکل زیر شما IC Gate OR را مشاهده می کنید:

۲- گیت AND ( و )

ساختمان گیت AND را با دو ورودی با استفاده از دیود مشاهده می کنید:

در این مدار در حالتی که یکی از دیود ها وصل باشد خروجی در حالت Low قرار می گیرد و فقط در صورتی خروجی در حالت High قرار می گیرد که دو کلید باز باشند یا در واقع ولتاژ ۵ ولت را به جای کلید ها قرار دهیم. مانند شکل زیر:

پس با توجه به مدار دیودی این گیت می توانیم یک جدول صحت برای این مدار تعریف کنیم :

در شکل زیر گیت AND را با نماد بین المللی و آمریکایی مشاهده می کنید:

همچنین نماد گیت AND را در استاندارد انگلیسی مشاهده می کنید:

در قسمت زیر جدول صحت گیت OR را مشاهده می کنید. در این گیت زمانی خروجی برابر ۱ می شود که تمام ورودی ها ۱ باشند و در غیر این صورت خروجی برابر صفر است.

برای نشان دادن این که دو متغیر AND شده اند به طور زیر عمل می کنیم :

یک دروازه AND می تواند بیش از دو ورودی داشته باشد ؛ برای مثال در شکل زیر یک دروازه با سه ورودی ، همراه با مدار معادل کلیدی آن را مشاهده می کنید.

در شکل زیر جدول صحت گیت AND با سه ورودی را مشاهده می کنید:

در شکل زیر آی سی گیت AND با دو ورودی را مشاهده می کنید :

۳- گیت NOT (نه)

مدار معادل این گیت را در شکل زیر مشاهده می کنید:

با توجه به مدار معادل این گیت می توانیم عملکرد گیت NOT را بررسی کنیم. هنگامی که ولتاژ ورودی این مدار صفر باشد ترانزیستور خاموش بوده و مانند کلید قطع عمل می کند. در این شرایط ولتاژ خروجی که همان ولتاژ کلکتور امیتر ترانزیستور است برابر VCC می باشد. اما با دادن ولتاژ به بیس ترانزیستور ، ترانزیستور روشن شده و مانند کلید بسته عمل می کند. در این شرایط ولتاژ کلکتور امیتر ترانزیستور حدود ۰٫۲ولت می باشد و در نتیجه خروجی در حالت LOW قرار می گیرد.

در شکل زیر جدول صحت این مدار را مشاهده می کنید:

همانطور که مشاهده می کنید ، در این گیت خروجی عکس ورودی است.

در شکل زیر نماد دروازه منطقی NOT را مشاهده می کنید:

در شکل زیر نماد گیت OR را در استاندارد انگلیسی مشاهده می کنید :

در شکل زیر آی سی گیت NOT را مشاهده می کنید :

دروازه های منطقی ترکیبی

با ترکیب برخی از دروازه های اساسی با یکدیگر دروازه های منطقی جدیدی ساخته می شوند که در ساخت مدار های الکترونیکی دیجیتالی و کامپیوتری می توانند بسیار مفید باشند. از مزایای دروازه های ترکیبی این است که به جای دو یا چند دروازه اساسی می توانیم فقط از یک دروازه استفاده کنیم.

۱- دروازه منطقی (NAND (Not AND

دروازه منطقی NAND از ترکیب دروازه AND ،NOT بوجود می آید. به عبارت دیگر ابتدا ورودی های این دو دروازه با یکدیگر AND می شوند و حاصل آن NOT می شود.

در شکل زیر عمکرد گیت NAND را مشاهده می کنید:

در شکل زیر نماد بین المللی گیت NAND را مشاهده می کنید :

در شکل زیر نماد انگلیسی گیت NAND را مشاهده می کنید :

در جدول زیر ، جدول صحت گیت NAND را مشاهده می کنید :

همانطور که در جدول بالا مشاهده می کنید خروجی دروازه منطقی در حالتی که حداقل یکی از ورودی ها در حالت ۰باشد ، در حالت ۱ منطقی قرار می گیرد.

این گیت نیز می تواند مانند گیت AND بیش از دو ورودی داشته باشد. در شکل زیر گیت NAND را با سه ورودی مشاهده می کنید:

در زیر جدول صحت گیت NAND با سه ورودی را مشاهده می کنید :

در شکل زیر آی سی گیت NAND را مشاهده می کنید :

۲ – دروازه منطقی NOR ( Not OR )

دروازه منطقی NOR از ترکیب دروازه های OR و NOT بوجود می آید. به عبارت دیگر ، ابتدا ورودی های این دروازه منطقی با یکدیگر OR می شوند و حاصل آن ( صفر یا یک است ) را NOT می کنند.

در شکل زیر عملکرد دروازه NOR را مشاهده می کنید :

برای ساده شدن ترسیم دروازه منطقی NOR می توان به جای شکل بالا از نماد زیر استفاده کرد :

در استاندارد انگلیسی از نماد زیر برای گیت NOR استفاده می کنند :

در جدول زیر ، جدول صحت گیت OR را مشاهده می کنید :

همانطور که در جدول بالا مشاهده می کنید در این گیت زمانی خروجی یک می باشد که ورودی های آن صفر باشند.

این گیت نیز می تواند بیش از دو ورودی داشته باشد. در زیر گیت OR را با سه ورودی به همراه جدول صحت مشاهده می کنید :

در شکل زیر آی سی گیت NOR با دو ورودی را مشاهده می کنید :

۳ – دروازه منطقی OR انحصاری (XOR (Exclusive OR

این گیت می تواند دو ورودی یا بیشتر را داشته باشد و در حالت دو ورودی زمانی خروجی آن یک است که دو ورودی در سطوح منطقی متفاوت باشند ( ورودی ها متفاوت باشند ).

در زیر مدار کلیدی این گیت را مشاهده می کنید :

در این مدار کلیدی کلید A دو کنتاکت را با هم کنترل و جا به جا می کند و کلید B هم به همین صورت است و زمانی VO برابر ۵ ولت می شود که وضعیت کلید ها متفاوت باشد.

در زیر جدول صحت این گیت را مشاهده می کنید :

در شکل زیر نماد گیت XOR را مشاهده می کنید :

همینطور نماد این گیت را در استاندارد انگلیسی مشاهده می کنید :

در تصویر زیر آی سی گیت XOR را مشاهده می کنید :

۴ – دروازه NOR انحصاری (XNOR (Exclusive NOR

این دروازه نیز مانند XOR فقط دو ورودی دارد و خروجی آن زمانی یک است که هردو ورودی آن در یک سطح منطقی باشند ( هر دو ورودی یک یا صفر باشند ). در شکل زیر مدار معادل کلیدی این گیت را مشاهده می کنید :

در شکل زیر جدول صحت مربوط به این گیت را مشاهده می کنید :

در تصویر زیر نماد استاندارد بین المللی گیت XNOR را مشاهده می کنید :

همچنین نماد انگلیسی این گیت در زیر آمده است :

دروازه منطقی بافر

این دروازه منطقی مانند گیت NOT یک ورودی و یک خروجی دارد. شکل زیر گیت بافر را نشان می دهد :

رابطه منطقی این گیت به صورت Y=A می باشد. گیت بافر معمولا به عنوان جداکننده بین دو طبقه استفاده می شود و از بارگذاری روی خروجی جلوگیری می نماید. در مدار های دیجیتالی گیت بافر وقتی در خروجی گیت اصلی قرار می گیرد ، تراز ولتاژ ورودی را عینا به خروجی مدار انتقال می دهد. در داخل گیت بافر مدار تقویت کننده جریان وجود دارد که میزان جریان دهی خروجی را افزایش می دهد.

در تصویر زیر خلاصه ای از گیت های منطقی را مشاهده می کنید :

مشخصات ویژه دروازه های منطقی

۱- fan-in

حداکثر تعداد ورودی که یک گیت منطقی می تواند قبول کند را fan-in می گویند. مثلا اگر یک گیت محدود به ۶ ورودی باشد ، می گوییم fan-in آن برابر ۶ می باشد.

۲- fan-out

حداکثر تعداد گیت هایی که می تواند از طریق خروجی یک گیت تغذیه شود را fan-out آن گیت گوییم. مثلا اگر یک گیت دارای fan-out برابر با ۵ باشد خروجی این گیت می تواند به ۵ ورودی گیت های مختلف یا یکسان وصل شود و آن ها را تغذیه کند ، به عبارت دیگر با اتصال ۵ گیت به خروجی گیت مورد نظر ، ولتاژ خروجی برای حالات منطقی صفر و یک حفظ می شود.

۳- حاشیه نویز Marginal noise

حاشیه نویز در یک گیت منطقی ، تاثیر دامنه نویز در ورودی مدار منطقی است. به عبارت دیگر میزان امنیتی است که با ظاهر شدن نویز ( هر نوع ولتاژ ناخواسته ) در ورودی یک مدار منطقی ، بتوانیم اطلاعات را بدون خطا انتقال دهیم و دریافت کنیم. به عبارت دیگر اگر دامنه ولتاژ نا خواسته بیشتر از حاشیه نویز تعریف شده باشد ، موجب تغییر وضعیت مدار شده و خروجی نادرست را نتییجه می دهد. مثلا اگر حاشیه نویز تعریف شده برابر ۰٫۸ ولت باشد در این حالت ، سیگنال نویز نباید به مقداری بیشتر از ۰٫۸ ولت برسد. در غیر این صورت موجب بروز خطایی در مدار خواهد شد.

در شکل زیر حاشیه نویز را در محدوده ولتاژ ورودی و محدوده ولتاژ خروجی مشاهده می کنید :

۴- تاخیر در انتشار Propagation delay

تاخیر در انتشار عبارت است از زمانی که خروجی یک دروازه منطقی لازم دارد تا تغییر ورودی را از یک حالت به حالت دیگر ظاهر نماید ، به عبارت دیگر هر چه تاخیر کمتر باشد سرعت انتقال اطلاعات بیشتر می شود.

بنابراین تاخیر در انتشار ، یکی از پارامتر های مهمی است که سرعت عملکرد یک سیستم منطقی را مشخص می کند.

زمان تاخیردر انتشار بسیار کم و در حدود چند نانو ثانیه است. هر چه تعداد گیت های سری در یک سیستم کمتر باشد تاخیر در انتشار کمتر است.

اولین دیدگاه را ثبت کنید